स्विचिंग पॉवर रिपल अपरिहार्य आहे. आमचा अंतिम उद्देश आउटपुट रिपलला सहन करण्यायोग्य पातळीपर्यंत कमी करणे आहे. हा उद्देश साध्य करण्यासाठी सर्वात मूलभूत उपाय म्हणजे रिपलची निर्मिती टाळणे. सर्वप्रथम आणि कारण.

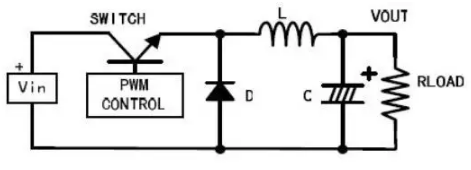

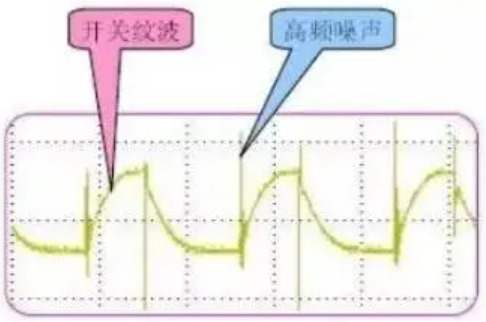

SWITCH च्या स्विचसह, इंडक्टन्स L मधील करंट देखील आउटपुट करंटच्या वैध मूल्यावर वर आणि खाली चढ-उतार होतो. म्हणून, आउटपुट एंडवर स्विच प्रमाणेच वारंवारता असलेली एक लहर देखील असेल. सामान्यतः, रिबरच्या लहरी याचा संदर्भ घेतात, जी आउटपुट कॅपेसिटर आणि ESR च्या क्षमतेशी संबंधित असते. या लहरींची वारंवारता स्विचिंग पॉवर सप्लाय सारखीच असते, ज्याची श्रेणी दहा ते शेकडो kHz असते.

याव्यतिरिक्त, स्विच सामान्यतः बायपोलर ट्रान्झिस्टर किंवा MOSFET वापरतो. कोणताही एक असला तरी, तो चालू केल्यावर आणि मृत झाल्यावर वाढ आणि घट वेळ असेल. यावेळी, सर्किटमध्ये कोणताही आवाज नसेल जो स्विचच्या वाढत्या कमी वेळेइतका किंवा काही वेळा असेल आणि सामान्यतः दहापट MHz असेल. त्याचप्रमाणे, डायोड D रिव्हर्स रिकव्हरीमध्ये आहे. समतुल्य सर्किट म्हणजे रेझिस्टन्स कॅपेसिटर आणि इंडक्टर्सची मालिका आहे, ज्यामुळे रेझोनन्स होईल आणि नॉइज फ्रिक्वेन्सी दहापट MHz आहे. या दोन नॉइजना सामान्यतः उच्च-फ्रिक्वेन्सी नॉइज म्हणतात आणि अॅम्प्लिट्यूड सहसा रिपलपेक्षा खूप मोठा असतो.

जर ते AC/DC कन्व्हर्टर असेल, तर वरील दोन लहरी (आवाज) व्यतिरिक्त, AC आवाज देखील असतो. वारंवारता ही इनपुट AC पॉवर सप्लायची वारंवारता असते, सुमारे 50-60Hz. एक को-मोड आवाज देखील असतो, कारण अनेक स्विचिंग पॉवर सप्लायचे पॉवर डिव्हाइस रेडिएटर म्हणून शेल वापरते, जे समतुल्य कॅपेसिटन्स निर्माण करते.

स्विचिंग पॉवर रिपल्सचे मापन

मूलभूत आवश्यकता:

ऑसिलोस्कोप एसी सह जोडणी

२०MHz बँडविड्थ मर्यादा

प्रोबचा ग्राउंड वायर अनप्लग करा

१.एसी कपलिंग म्हणजे सुपरपोझिशन डीसी व्होल्टेज काढून टाकणे आणि अचूक वेव्हफॉर्म मिळवणे.

२. २० मेगाहर्ट्झ बँडविड्थ मर्यादा उघडणे म्हणजे उच्च-फ्रिक्वेन्सी आवाजाचा हस्तक्षेप रोखणे आणि त्रुटी टाळणे. उच्च-फ्रिक्वेन्सी रचनेचे मोठेपणा मोठे असल्याने, मोजताना ते काढून टाकले पाहिजे.

३. ऑसिलोस्कोप प्रोबची ग्राउंड क्लिप अनप्लग करा आणि अडथळा कमी करण्यासाठी ग्राउंड मापन मापन वापरा. अनेक विभागांमध्ये ग्राउंड रिंग नसतात. परंतु ते पात्र आहे की नाही हे ठरवताना हा घटक विचारात घ्या.

दुसरा मुद्दा म्हणजे ५०Ω टर्मिनल वापरणे. ऑसिलोस्कोपच्या माहितीनुसार, ५०Ω मॉड्यूल म्हणजे डीसी घटक काढून टाकणे आणि एसी घटक अचूकपणे मोजणे. तथापि, अशा विशेष प्रोबसह काही ऑसिलोस्कोप आहेत. बहुतेक प्रकरणांमध्ये, १००kΩ ते १०MΩ पर्यंतच्या प्रोबचा वापर केला जातो, जो तात्पुरता अस्पष्ट आहे.

स्विचिंग रिपल मोजताना वरील मूलभूत खबरदारी आहे. जर ऑसिलोस्कोप प्रोब थेट आउटपुट पॉइंटच्या संपर्कात नसेल, तर ते वळवलेल्या रेषा किंवा 50Ω कोएक्सियल केबल्सने मोजले पाहिजे.

उच्च-फ्रिक्वेन्सी आवाज मोजताना, ऑसिलोस्कोपचा पूर्ण बँड साधारणपणे शेकडो मेगा ते गीगाहर्ट्झ पातळीचा असतो. इतर वरील प्रमाणेच असतात. कदाचित वेगवेगळ्या कंपन्यांच्या वेगवेगळ्या चाचणी पद्धती असतील. अंतिम विश्लेषणात, तुम्हाला तुमचे चाचणी निकाल माहित असले पाहिजेत.

ऑसिलोस्कोप बद्दल:

काही डिजिटल ऑसिलोस्कोप हस्तक्षेप आणि साठवण खोलीमुळे तरंगांचे योग्यरित्या मोजमाप करू शकत नाहीत. यावेळी, ऑसिलोस्कोप बदलला पाहिजे. कधीकधी जुन्या सिम्युलेशन ऑसिलोस्कोपची बँडविड्थ फक्त दहापट मेगा असली तरी, त्याची कार्यक्षमता डिजिटल ऑसिलोस्कोपपेक्षा चांगली असते.

स्विचिंग पॉवर रिपल्सचा प्रतिबंध

तरंग बदलण्यासाठी, सैद्धांतिकदृष्ट्या आणि प्रत्यक्षात अस्तित्वात आहेत. ते दाबण्याचे किंवा कमी करण्याचे तीन मार्ग आहेत:

१. इंडक्टन्स आणि आउटपुट कॅपेसिटर फिल्टरिंग वाढवा

स्विचिंग पॉवर सप्लायच्या सूत्रानुसार, प्रेरक प्रेरकतेचे वर्तमान चढउतार आकार आणि प्रेरकतेचे मूल्य व्यस्त प्रमाणात होतात आणि आउटपुट तरंग आणि आउटपुट कॅपेसिटर व्यस्त प्रमाणात असतात. म्हणून, इलेक्ट्रिकल आणि आउटपुट कॅपेसिटर वाढवल्याने तरंग कमी होऊ शकतात.

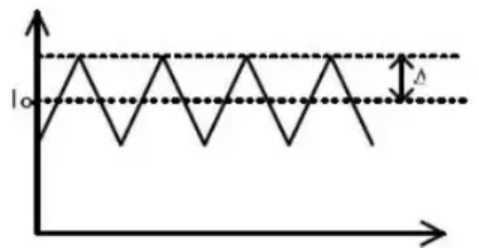

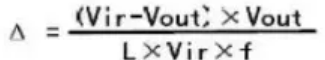

वरील चित्र स्विचिंग पॉवर सप्लाय इंडक्टर L मधील वर्तमान तरंगरूप आहे. त्याचा तरंग प्रवाह △ i खालील सूत्रावरून मोजता येतो:

असे दिसून येते की L मूल्य वाढवणे किंवा स्विचिंग वारंवारता वाढवणे इंडक्टन्समधील वर्तमान चढउतार कमी करू शकते.

त्याचप्रमाणे, आउटपुट रिपल्स आणि आउटपुट कॅपेसिटरमधील संबंध: VRIPPLE = IMAX/(CO × F). हे दिसून येते की आउटपुट कॅपेसिटर मूल्य वाढवल्याने रिपल्स कमी होऊ शकतात.

मोठ्या क्षमतेचा उद्देश साध्य करण्यासाठी आउटपुट कॅपेसिटन्ससाठी अॅल्युमिनियम इलेक्ट्रोलाइटिक कॅपेसिटर वापरणे ही नेहमीची पद्धत आहे. तथापि, उच्च-फ्रिक्वेन्सी आवाज दाबण्यात इलेक्ट्रोलाइटिक कॅपेसिटर फारसे प्रभावी नाहीत आणि ESR तुलनेने मोठा आहे, म्हणून ते अॅल्युमिनियम इलेक्ट्रोलाइटिक कॅपेसिटरची कमतरता भरून काढण्यासाठी त्याच्या शेजारी एक सिरेमिक कॅपेसिटर जोडेल.

त्याच वेळी, जेव्हा वीजपुरवठा कार्यरत असतो, तेव्हा इनपुट टर्मिनलचा व्होल्टेज VIN बदलत नाही, परंतु स्विचसह करंट बदलतो. यावेळी, इनपुट पॉवर सप्लाय करंट वेल प्रदान करत नाही, सामान्यतः करंट इनपुट टर्मिनलजवळ (उदाहरणार्थ, बक प्रकार स्विचजवळ असतो), आणि करंट प्रदान करण्यासाठी कॅपेसिटन्सला जोडतो.

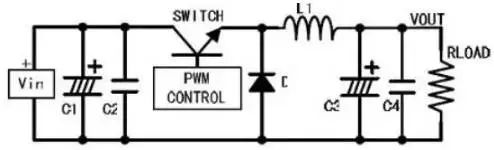

हे काउंटरमेजर लागू केल्यानंतर, बक स्विच पॉवर सप्लाय खालील आकृतीमध्ये दाखवला आहे:

वरील पद्धत तरंग कमी करण्यापुरती मर्यादित आहे. व्हॉल्यूम मर्यादेमुळे, इंडक्टन्स फार मोठा होणार नाही; आउटपुट कॅपेसिटर एका विशिष्ट प्रमाणात वाढतो आणि तरंग कमी करण्यावर कोणताही स्पष्ट परिणाम होत नाही; स्विचिंग फ्रिक्वेन्सी वाढल्याने स्विच लॉस वाढेल. म्हणून जेव्हा आवश्यकता कठोर असतात तेव्हा ही पद्धत फारशी चांगली नसते.

स्विचिंग पॉवर सप्लायच्या तत्त्वांसाठी, तुम्ही विविध प्रकारच्या स्विचिंग पॉवर डिझाइन मॅन्युअलचा संदर्भ घेऊ शकता.

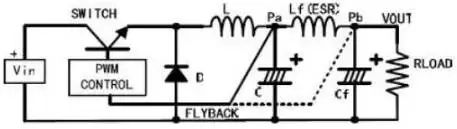

२. टू-लेव्हल फिल्टरिंग म्हणजे फर्स्ट-लेव्हल एलसी फिल्टर जोडणे

एलसी फिल्टरचा नॉइज रिपलवर होणारा प्रतिबंधात्मक परिणाम तुलनेने स्पष्ट आहे. काढायच्या रिपल फ्रिक्वेन्सीनुसार, फिल्टर सर्किट तयार करण्यासाठी योग्य इंडक्टर कॅपेसिटर निवडा. साधारणपणे, ते रिपल चांगल्या प्रकारे कमी करू शकते. या प्रकरणात, तुम्हाला फीडबॅक व्होल्टेजच्या सॅम्पलिंग पॉइंटचा विचार करणे आवश्यक आहे. (खाली दाखवल्याप्रमाणे)

एलसी फिल्टर (पीए) च्या आधी सॅम्पलिंग पॉइंट निवडला जातो आणि आउटपुट व्होल्टेज कमी होईल. कोणत्याही इंडक्टन्समध्ये डीसी रेझिस्टन्स असल्याने, जेव्हा करंट आउटपुट असेल तेव्हा इंडक्टन्समध्ये व्होल्टेज ड्रॉप होईल, ज्यामुळे पॉवर सप्लायच्या आउटपुट व्होल्टेजमध्ये घट होईल. आणि हा व्होल्टेज ड्रॉप आउटपुट करंटसह बदलतो.

एलसी फिल्टर (पीबी) नंतर सॅम्पलिंग पॉइंट निवडला जातो, जेणेकरून आउटपुट व्होल्टेज आपल्याला हवा असलेला व्होल्टेज असेल. तथापि, पॉवर सिस्टममध्ये एक इंडक्टन्स आणि कॅपेसिटर सादर केला जातो, ज्यामुळे सिस्टम अस्थिरता निर्माण होऊ शकते.

३. स्विचिंग पॉवर सप्लायच्या आउटपुटनंतर, LDO फिल्टरिंग कनेक्ट करा.

तरंग आणि आवाज कमी करण्याचा हा सर्वात प्रभावी मार्ग आहे. आउटपुट व्होल्टेज स्थिर आहे आणि मूळ अभिप्राय प्रणाली बदलण्याची आवश्यकता नाही, परंतु ते सर्वात किफायतशीर आणि सर्वाधिक वीज वापर देखील आहे.

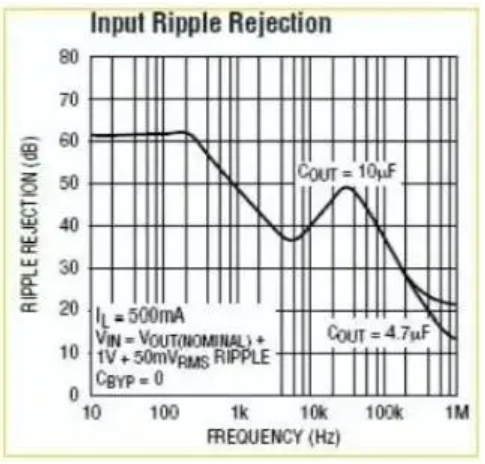

कोणत्याही LDO मध्ये एक निर्देशक असतो: आवाज दमन गुणोत्तर. हा एक वारंवारता-DB वक्र आहे, जसे खालील आकृतीत दाखवले आहे की LT3024 LT3024 चा वक्र आहे.

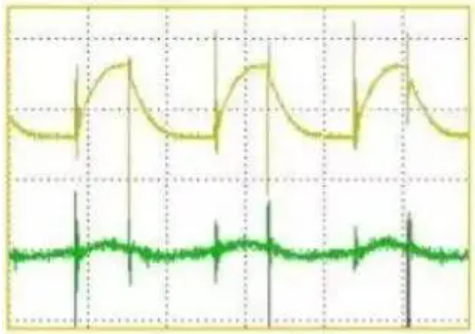

LDO नंतर, स्विचिंग रिपल साधारणपणे 10mV पेक्षा कमी असते. खालील आकृती LDO च्या आधी आणि नंतरच्या रिपलची तुलना आहे:

वरील आकृतीतील वक्र आणि डावीकडील तरंगरूप यांच्या तुलनेत, हे दिसून येते की शेकडो KHz च्या स्विचिंग लहरींसाठी LDO चा प्रतिबंधात्मक प्रभाव खूप चांगला आहे. परंतु उच्च वारंवारता श्रेणीमध्ये, LDO चा प्रभाव इतका आदर्श नाही.

तरंग कमी करा. स्विचिंग पॉवर सप्लायचे पीसीबी वायरिंग देखील महत्त्वाचे आहे. उच्च-फ्रिक्वेन्सी आवाजासाठी, उच्च-फ्रिक्वेन्सीच्या मोठ्या वारंवारतेमुळे, जरी पोस्ट-स्टेज फिल्टरिंगचा विशिष्ट परिणाम होत असला तरी, परिणाम स्पष्ट नाही. या संदर्भात विशेष अभ्यास आहेत. डायोड आणि कॅपेसिटन्स सी किंवा आरसीवर असणे किंवा इंडक्टन्सला मालिकेत जोडणे हा सोपा दृष्टिकोन आहे.

वरील आकृती प्रत्यक्ष डायोडच्या समतुल्य सर्किटची आहे. जेव्हा डायोड हाय-स्पीड असतो, तेव्हा परजीवी पॅरामीटर्स विचारात घेतले पाहिजेत. डायोडच्या रिव्हर्स रिकव्हरी दरम्यान, समतुल्य इंडक्टन्स आणि समतुल्य कॅपेसिटन्स एक आरसी ऑसिलेटर बनले, ज्यामुळे उच्च-फ्रिक्वेन्सी ऑसिलेशन निर्माण होते. हे उच्च-फ्रिक्वेन्सी ऑसिलेशन दाबण्यासाठी, डायोडच्या दोन्ही टोकांना कॅपेसिटन्स सी किंवा आरसी बफर नेटवर्क जोडणे आवश्यक आहे. प्रतिरोध सामान्यतः 10Ω-100 ω असतो आणि कॅपेसिटन्स 4.7PF-2.2NF असतो.

डायोड C किंवा RC वरील कॅपेसिटन्स C किंवा RC वारंवार चाचण्यांद्वारे निश्चित केले जाऊ शकते. जर ते योग्यरित्या निवडले नाही तर ते अधिक तीव्र दोलन निर्माण करेल.

पोस्ट वेळ: जुलै-०८-२०२३