सर्वसाधारणपणे, लॅमिनेटेड डिझाइनसाठी दोन मुख्य नियम आहेत:

१. प्रत्येक राउटिंग लेयरला एक समीप संदर्भ लेयर (वीज पुरवठा किंवा निर्मिती) असणे आवश्यक आहे;

२. मोठ्या कपलिंग कॅपेसिटन्ससाठी लगतचा मुख्य पॉवर लेयर आणि ग्राउंड कमीत कमी अंतरावर ठेवावे;

दोन-स्तर ते आठ-स्तरांच्या स्टॅकचे उदाहरण खालीलप्रमाणे आहे:

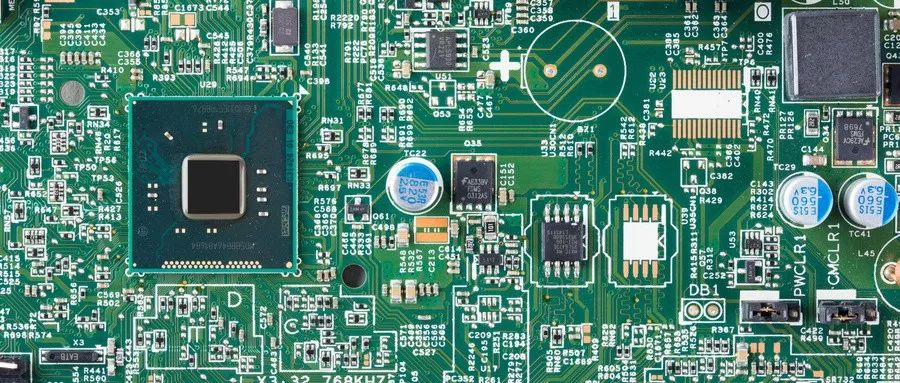

A. सिंगल-साइड पीसीबी बोर्ड आणि डबल-साइड पीसीबी बोर्ड लॅमिनेटेड

दोन थरांसाठी, थरांची संख्या कमी असल्याने, लॅमिनेशनची समस्या नाही. ईएमआय रेडिएशन नियंत्रण प्रामुख्याने वायरिंग आणि लेआउटवरून विचारात घेतले जाते;

सिंगल-लेयर आणि डबल-लेयर प्लेट्सची इलेक्ट्रोमॅग्नेटिक कंपॅटिबिलिटी अधिकाधिक ठळक होत चालली आहे. या घटनेचे मुख्य कारण म्हणजे सिग्नल लूपचे क्षेत्रफळ खूप मोठे आहे, जे केवळ मजबूत इलेक्ट्रोमॅग्नेटिक रेडिएशन निर्माण करत नाही तर सर्किटला बाह्य हस्तक्षेपासाठी संवेदनशील बनवते. रेषेची इलेक्ट्रोमॅग्नेटिक कंपॅटिबिलिटी सुधारण्याचा सर्वात सोपा मार्ग म्हणजे क्रिटिकल सिग्नलचे लूप एरिया कमी करणे.

क्रिटिकल सिग्नल: इलेक्ट्रोमॅग्नेटिक कंपॅटिबिलिटीच्या दृष्टिकोनातून, क्रिटिकल सिग्नल म्हणजे प्रामुख्याने असे सिग्नल जे तीव्र रेडिएशन निर्माण करतात आणि बाह्य जगासाठी संवेदनशील असतात. जे सिग्नल तीव्र रेडिएशन निर्माण करू शकतात ते सहसा नियतकालिक सिग्नल असतात, जसे की घड्याळांचे किंवा पत्त्यांचे कमी सिग्नल. हस्तक्षेप संवेदनशील सिग्नल म्हणजे असे सिग्नल ज्यांचे अॅनालॉग सिग्नलचे प्रमाण कमी असते.

१०KHz पेक्षा कमी फ्रिक्वेन्सी सिम्युलेशन डिझाइनमध्ये सिंगल आणि डबल लेयर प्लेट्स सहसा वापरल्या जातात:

१) पॉवर केबल्सना एकाच थरावर रेडियल पद्धतीने रूट करा आणि रेषांच्या लांबीची बेरीज कमीत कमी करा;

२) वीजपुरवठा आणि ग्राउंड वायर एकमेकांच्या जवळ चालताना; की सिग्नल वायरजवळ शक्य तितक्या जवळ एक ग्राउंड वायर ठेवा. अशा प्रकारे, एक लहान लूप क्षेत्र तयार होते आणि बाह्य हस्तक्षेपासाठी डिफरेंशियल मोड रेडिएशनची संवेदनशीलता कमी होते. जेव्हा सिग्नल वायरच्या शेजारी ग्राउंड वायर जोडली जाते, तेव्हा सर्वात लहान क्षेत्रफळ असलेले सर्किट तयार होते आणि सिग्नल करंट इतर ग्राउंड मार्गाऐवजी या सर्किटमधून मार्गस्थ केला पाहिजे.

३) जर ते दुहेरी-स्तरीय सर्किट बोर्ड असेल, तर ते सर्किट बोर्डच्या दुसऱ्या बाजूला, खालील सिग्नल लाईनच्या जवळ, सिग्नल लाईनच्या कापडाच्या बाजूने एक ग्राउंड वायर, शक्य तितकी रुंदीची रेषा असू शकते. परिणामी सर्किट क्षेत्रफळ सिग्नल लाईनच्या लांबीने गुणाकार केलेल्या सर्किट बोर्डच्या जाडीइतके असते.

ब. चार थरांचे लॅमिनेशन

१. सिग-जीएनडी (पीडब्ल्यूआर)-पीडब्ल्यूआर (जीएनडी)-एसआयजी;

२. जीएनडी-एसआयजी(पीडब्ल्यूआर)-एसआयजी(पीडब्ल्यूआर)-जीएनडी;

या दोन्ही लॅमिनेटेड डिझाईन्ससाठी, संभाव्य समस्या पारंपारिक १.६ मिमी (६२ मिली) प्लेट जाडीची आहे. थरांमधील अंतर मोठे होईल, जे केवळ प्रतिबाधा नियंत्रित करण्यासाठी, इंटरलेयर कपलिंग आणि शील्डिंगसाठी अनुकूल नाही; विशेषतः, वीज पुरवठा थरांमधील मोठे अंतर प्लेट कॅपेसिटन्स कमी करते आणि आवाज फिल्टरिंगसाठी अनुकूल नाही.

पहिल्या योजनेसाठी, बोर्डवर मोठ्या संख्येने चिप्स असल्यास ते सहसा वापरले जाते. या योजनेमुळे चांगले SI कार्यप्रदर्शन मिळू शकते, परंतु EMI कार्यप्रदर्शन इतके चांगले नाही, जे प्रामुख्याने वायरिंग आणि इतर तपशीलांद्वारे नियंत्रित केले जाते. मुख्य लक्ष: निर्मिती सर्वात दाट सिग्नल लेयरच्या सिग्नल लेयरमध्ये ठेवली जाते, जी रेडिएशन शोषण्यास आणि दडपण्यास अनुकूल असते; 20H नियम प्रतिबिंबित करण्यासाठी प्लेट क्षेत्र वाढवा.

दुसऱ्या योजनेसाठी, सामान्यतः बोर्डवरील चिप घनता कमी असते आणि आवश्यक पॉवर कॉपर कोटिंग ठेवण्यासाठी चिपभोवती पुरेसा क्षेत्र असतो तेव्हा याचा वापर केला जातो. या योजनेत, PCB चा बाह्य थर संपूर्ण स्ट्रॅटम असतो आणि मधले दोन थर सिग्नल/पॉवर लेयर असतात. सिग्नल लेयरवरील वीज पुरवठा एका रुंद रेषेने राउट केला जातो, ज्यामुळे वीज पुरवठ्याच्या प्रवाहाचा मार्ग प्रतिबाधा कमी होऊ शकतो आणि सिग्नल मायक्रोस्ट्रिप मार्गाचा प्रतिबाधा देखील कमी असतो आणि बाह्य थरातून आतील सिग्नल रेडिएशनला देखील संरक्षित करू शकतो. EMI नियंत्रण दृष्टिकोनातून, ही उपलब्ध असलेली सर्वोत्तम 4-लेयर PCB रचना आहे.

मुख्य लक्ष: सिग्नलचे मधले दोन थर, पॉवर मिक्सिंग लेयर स्पेसिंग उघडे असावे, रेषेची दिशा उभ्या असावी, क्रॉसटॉक टाळा; योग्य नियंत्रण पॅनेल क्षेत्र, 20H नियम प्रतिबिंबित करते; जर तारांचा प्रतिबाधा नियंत्रित करायचा असेल, तर वीज पुरवठा आणि जमिनीच्या तांब्याच्या बेटाखाली तारा अतिशय काळजीपूर्वक ठेवा. याव्यतिरिक्त, डीसी आणि कमी फ्रिक्वेन्सी कनेक्टिव्हिटी सुनिश्चित करण्यासाठी वीज पुरवठा किंवा तांबे घालणे शक्य तितके एकमेकांशी जोडलेले असावे.

क. प्लेट्सच्या सहा थरांचे लॅमिनेशन

उच्च चिप घनता आणि उच्च घड्याळ वारंवारता असलेल्या डिझाइनसाठी, 6-स्तरीय बोर्डची रचना विचारात घेतली पाहिजे. लॅमिनेशन पद्धत शिफारसित आहे:

१.सिग-जीएनडी-सिग-पीडब्ल्यूआर-जीएनडी-सिग;

या योजनेसाठी, लॅमिनेशन योजना चांगली सिग्नल अखंडता प्राप्त करते, सिग्नल लेयर ग्राउंडिंग लेयरला लागून असल्याने, पॉवर लेयर ग्राउंडिंग लेयरशी जोडलेला असल्याने, प्रत्येक राउटिंग लेयरचा प्रतिबाधा चांगल्या प्रकारे नियंत्रित केला जाऊ शकतो आणि दोन्ही लेयर चुंबकीय रेषा चांगल्या प्रकारे शोषू शकतात. याव्यतिरिक्त, ते पूर्ण वीज पुरवठा आणि निर्मितीच्या स्थितीत प्रत्येक सिग्नल लेयरसाठी चांगला परतीचा मार्ग प्रदान करू शकते.

२. जीएनडी-सिग-जीएनडी-पीडब्ल्यूआर-सिग-जीएनडी;

या योजनेसाठी, ही योजना फक्त अशाच बाबतीत लागू होते जिथे उपकरणाची घनता खूप जास्त नसते. या थरात वरच्या थराचे सर्व फायदे आहेत आणि वरच्या आणि खालच्या थराचे ग्राउंड प्लेन तुलनेने पूर्ण आहे, जे चांगले शिल्डिंग लेयर म्हणून वापरले जाऊ शकते. हे लक्षात ठेवणे महत्वाचे आहे की पॉवर लेयर मुख्य घटक प्लेन नसलेल्या लेयरजवळ असावा, कारण खालचा प्लेन अधिक पूर्ण असेल. म्हणून, EMI कामगिरी पहिल्या योजनेपेक्षा चांगली आहे.

सारांश: सहा-स्तरीय बोर्डच्या योजनेसाठी, चांगली शक्ती आणि ग्राउंड कपलिंग मिळविण्यासाठी पॉवर लेयर आणि ग्राउंडमधील अंतर कमीत कमी केले पाहिजे. तथापि, प्लेटची जाडी 62 मिली आणि थरांमधील अंतर कमी केले असले तरी, मुख्य उर्जा स्त्रोत आणि ग्राउंड लेयरमधील अंतर नियंत्रित करणे अद्याप कठीण आहे. पहिल्या योजनेच्या आणि दुसऱ्या योजनेच्या तुलनेत, दुसऱ्या योजनेची किंमत खूप जास्त आहे. म्हणून, जेव्हा आपण स्टॅक करतो तेव्हा आपण सहसा पहिला पर्याय निवडतो. डिझाइन दरम्यान, 20H नियम आणि मिरर लेयर नियमांचे पालन करा.

ड. आठ थरांचे लॅमिनेशन

१, खराब इलेक्ट्रोमॅग्नेटिक शोषण क्षमता आणि मोठ्या पॉवर प्रतिबाधामुळे, लॅमिनेशनचा हा चांगला मार्ग नाही. त्याची रचना खालीलप्रमाणे आहे:

१.सिग्नल १ घटक पृष्ठभाग, मायक्रोस्ट्रिप वायरिंग थर

२.सिग्नल २ अंतर्गत मायक्रोस्ट्रिप राउटिंग लेयर, चांगला राउटिंग लेयर (X दिशा)

३.जमिनी

४.सिग्नल ३ स्ट्रिप लाईन राउटिंग लेयर, चांगला राउटिंग लेयर (Y दिशा)

५.सिग्नल ४ केबल राउटिंग लेयर

६.शक्ती

७.सिग्नल ५ अंतर्गत मायक्रोस्ट्रिप वायरिंग थर

८.सिग्नल ६ मायक्रोस्ट्रिप वायरिंग लेयर

२. हे तिसऱ्या स्टॅकिंग मोडचे एक प्रकार आहे. संदर्भ थर जोडल्यामुळे, त्याची EMI कामगिरी चांगली आहे आणि प्रत्येक सिग्नल थराचा वैशिष्ट्यपूर्ण प्रतिबाधा चांगल्या प्रकारे नियंत्रित केला जाऊ शकतो.

१.सिग्नल १ घटक पृष्ठभाग, मायक्रोस्ट्रिप वायरिंग थर, चांगला वायरिंग थर

२.जमिनीचा थर, चांगली इलेक्ट्रोमॅग्नेटिक वेव्ह शोषण क्षमता

३.सिग्नल २ केबल राउटिंग लेयर. चांगला केबल राउटिंग लेयर

४. पॉवर लेयर आणि खालील स्तर उत्कृष्ट इलेक्ट्रोमॅग्नेटिक शोषण तयार करतात ५. ग्राउंड लेयर

६.सिग्नल ३ केबल राउटिंग लेयर. चांगला केबल राउटिंग लेयर

७. मोठ्या पॉवर इम्पेडन्ससह पॉवर फॉर्मेशन

८.सिग्नल ४ मायक्रोस्ट्रिप केबल लेयर. चांगला केबल लेयर

३, सर्वोत्तम स्टॅकिंग मोड, कारण मल्टी-लेयर ग्राउंड रेफरन्स प्लेनच्या वापरामुळे भूचुंबकीय शोषण क्षमता खूप चांगली असते.

१.सिग्नल १ घटक पृष्ठभाग, मायक्रोस्ट्रिप वायरिंग थर, चांगला वायरिंग थर

२.जमिनीचा थर, चांगली इलेक्ट्रोमॅग्नेटिक वेव्ह शोषण क्षमता

३.सिग्नल २ केबल राउटिंग लेयर. चांगला केबल राउटिंग लेयर

४. पॉवर लेयर आणि खालील स्तर उत्कृष्ट इलेक्ट्रोमॅग्नेटिक शोषण तयार करतात ५. ग्राउंड लेयर

६.सिग्नल ३ केबल राउटिंग लेयर. चांगला केबल राउटिंग लेयर

७. जमिनीवरील थर, चांगले इलेक्ट्रोमॅग्नेटिक वेव्ह शोषण क्षमता

८.सिग्नल ४ मायक्रोस्ट्रिप केबल लेयर. चांगला केबल लेयर

किती लेयर्स वापरायचे आणि लेयर्स कसे वापरायचे याची निवड बोर्डवरील सिग्नल नेटवर्क्सची संख्या, डिव्हाइसची घनता, पिन घनता, सिग्नल फ्रिक्वेन्सी, बोर्ड आकार आणि इतर अनेक घटकांवर अवलंबून असते. आपल्याला हे घटक विचारात घेणे आवश्यक आहे. सिग्नल नेटवर्क्सची संख्या जितकी जास्त असेल तितकी डिव्हाइसची घनता जास्त असेल, पिन घनता जास्त असेल तितकी सिग्नल डिझाइनची वारंवारता शक्य तितकी जास्त स्वीकारली पाहिजे. चांगल्या EMI कामगिरीसाठी प्रत्येक सिग्नल लेयरचा स्वतःचा संदर्भ लेयर असल्याची खात्री करणे चांगले.

पोस्ट वेळ: जून-२६-२०२३