डीआयपी समजून घ्या

DIP हे एक प्लग-इन आहे. अशा प्रकारे पॅक केलेल्या चिप्समध्ये पिनच्या दोन ओळी असतात, ज्या थेट DIP स्ट्रक्चर असलेल्या चिप सॉकेटमध्ये वेल्ड केल्या जाऊ शकतात किंवा समान संख्येच्या छिद्रांसह वेल्डिंग पोझिशन्सवर वेल्ड केल्या जाऊ शकतात. PCB बोर्ड छिद्र वेल्डिंग करणे खूप सोयीचे आहे आणि मदरबोर्डशी चांगली सुसंगतता आहे, परंतु त्याचे पॅकेजिंग क्षेत्र आणि जाडी तुलनेने मोठी असल्याने आणि घालण्याच्या आणि काढण्याच्या प्रक्रियेत पिन खराब होणे सोपे आहे, कमी विश्वासार्हता आहे.

DIP हे सर्वात लोकप्रिय प्लग-इन पॅकेज आहे, अनुप्रयोग श्रेणीमध्ये मानक लॉजिक आयसी, मेमरी एलएसआय, मायक्रोकॉम्प्युटर सर्किट्स इत्यादींचा समावेश आहे. स्मॉल प्रोफाइल पॅकेज (SOP), SOJ (J-प्रकार पिन स्मॉल प्रोफाइल पॅकेज), TSOP (पातळ लहान प्रोफाइल पॅकेज), VSOP (खूप लहान प्रोफाइल पॅकेज), SSOP (कमी केलेले SOP), TSSOP (पातळ कमी केलेले SOP) आणि SOT (लहान प्रोफाइल ट्रान्झिस्टर), SOIC (लहान प्रोफाइल इंटिग्रेटेड सर्किट) इत्यादींपासून बनलेले आहे.

डीआयपी डिव्हाइस असेंब्ली डिझाइनमधील दोष

पीसीबी पॅकेज होल डिव्हाइसपेक्षा मोठा आहे.

PCB प्लग-इन होल आणि पॅकेज पिन होल स्पेसिफिकेशननुसार काढले जातात. प्लेट बनवताना होलमध्ये कॉपर प्लेटिंगची आवश्यकता असल्याने, सामान्य सहनशीलता प्लस किंवा मायनस 0.075 मिमी असते. जर PCB पॅकेजिंग होल भौतिक उपकरणाच्या पिनपेक्षा खूप मोठा असेल, तर त्यामुळे उपकरण सैल होणे, अपुरे टिन, एअर वेल्डिंग आणि इतर गुणवत्ता समस्या उद्भवतील.

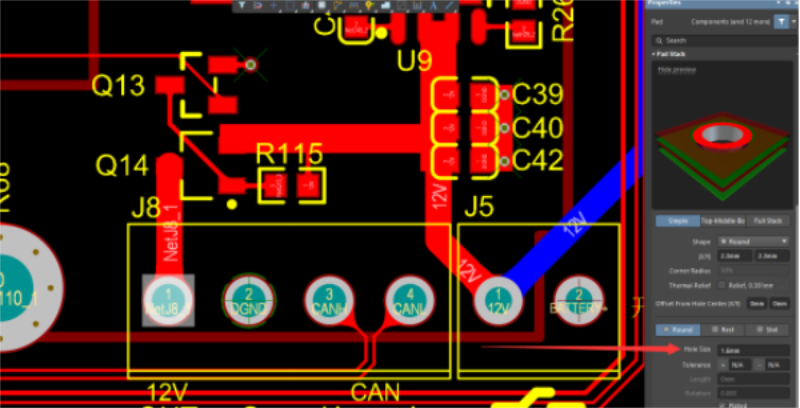

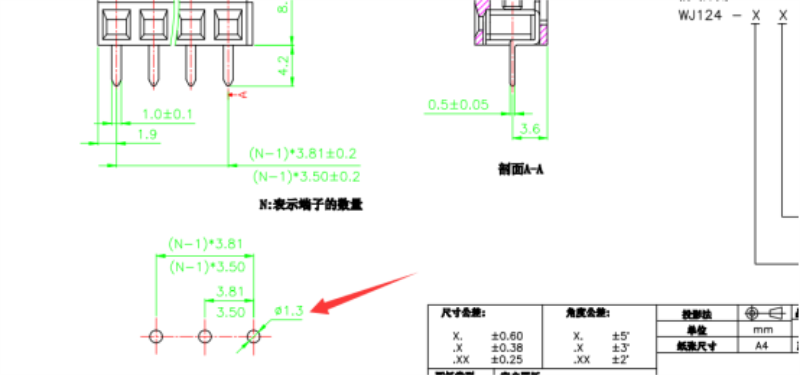

खालील आकृती पहा, WJ124-3.81-4P_WJ124-3.81-4P (KANGNEX) वापरून डिव्हाइस पिन 1.3 मिमी आहे, PCB पॅकेजिंग होल 1.6 मिमी आहे, छिद्र खूप मोठे आहे ज्यामुळे ओव्हरवेव्ह वेल्डिंग स्पेस टाइम वेल्डिंग होऊ शकते.

आकृतीसोबत जोडलेले आहे, डिझाइन आवश्यकतांनुसार WJ124-3.81-4P_WJ124-3.81-4P (KANGNEX) घटक खरेदी करा, पिन १.३ मिमी बरोबर आहे.

पीसीबी पॅकेज होल डिव्हाइसपेक्षा लहान आहे

प्लग-इन, पण होल नसेल तांबे, जर ते सिंगल आणि डबल पॅनल असेल तर तुम्ही ही पद्धत वापरू शकता, सिंगल आणि डबल पॅनल हे बाह्य विद्युत वाहक असतात, सोल्डर हे वाहक असू शकतात; मल्टीलेयर बोर्डचे प्लग-इन होल लहान असते आणि पीसीबी बोर्ड फक्त आतील थरात विद्युत वाहकता असेल तरच पुन्हा बनवता येते, कारण आतील थराचे वाहकता रीमिंगद्वारे दुरुस्त करता येत नाही.

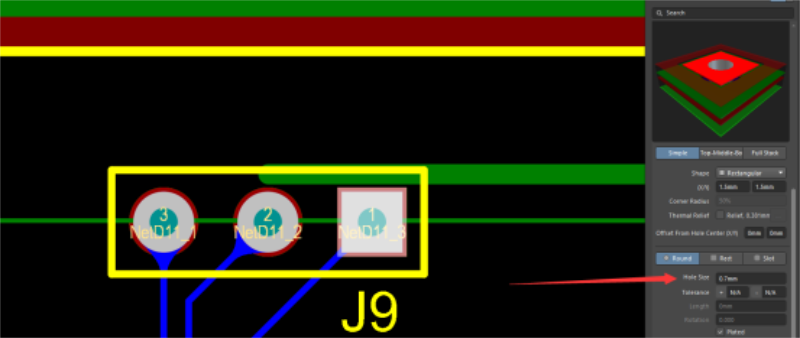

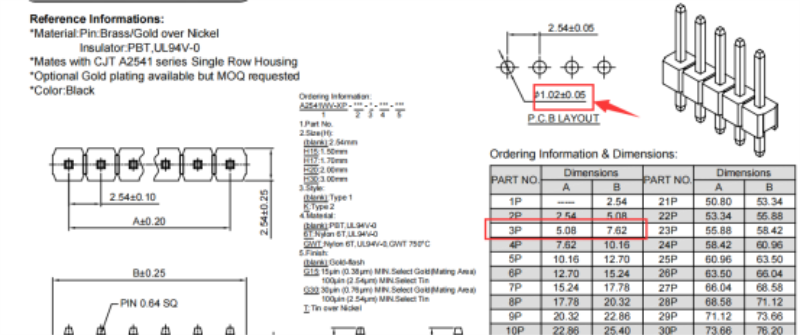

खालील आकृतीत दाखवल्याप्रमाणे, A2541Hwv-3P_A2541HWV-3P (CJT) चे घटक डिझाइन आवश्यकतांनुसार खरेदी केले जातात. पिन 1.0 मिमी आहे आणि PCB सीलिंग पॅड होल 0.7 मिमी आहे, ज्यामुळे ते घालता येत नाही.

A2541Hwv-3P_A2541HWV-3P (CJT) चे घटक डिझाइन आवश्यकतांनुसार खरेदी केले आहेत. पिन 1.0 मिमी बरोबर आहे.

पॅकेज पिन स्पेसिंग डिव्हाइस स्पेसिंगपेक्षा वेगळे आहे

डीआयपी उपकरणाच्या पीसीबी सीलिंग पॅडमध्ये केवळ पिनइतकेच छिद्र नसते, तर पिन छिद्रांमधील अंतर देखील समान असणे आवश्यक आहे. जर पिन छिद्रे आणि उपकरणांमधील अंतर विसंगत असेल, तर समायोजित करण्यायोग्य पाय अंतर असलेल्या भागांशिवाय, उपकरण घालता येत नाही.

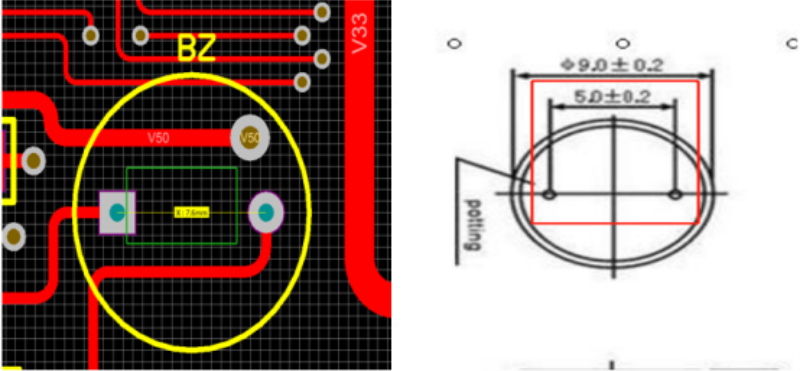

खालील आकृतीत दाखवल्याप्रमाणे, PCB पॅकेजिंगचे पिन होल अंतर 7.6 मिमी आहे आणि खरेदी केलेल्या घटकांचे पिन होल अंतर 5.0 मिमी आहे. 2.6 मिमीच्या फरकामुळे डिव्हाइस निरुपयोगी होते.

पीसीबी पॅकेजिंग होल खूप जवळ आहेत.

पीसीबी डिझाइन, ड्रॉइंग आणि पॅकेजिंगमध्ये, पिन होलमधील अंतराकडे लक्ष देणे आवश्यक आहे. जरी बेअर प्लेट तयार करता येत असली तरी, पिन होलमधील अंतर कमी असले तरी, वेव्ह सोल्डरिंगद्वारे असेंब्ली दरम्यान टिन शॉर्ट सर्किट होणे सोपे आहे.

खालील आकृतीत दाखवल्याप्रमाणे, पिनच्या अंतरापेक्षा कमी अंतरामुळे शॉर्ट सर्किट होऊ शकते. सोल्डरिंग टिनमध्ये शॉर्ट सर्किट होण्याची अनेक कारणे आहेत. जर डिझाइनच्या शेवटी असेंब्लीबिलिटी आधीच रोखता आली तर समस्यांचे प्रमाण कमी करता येते.

डीआयपी डिव्हाइस पिन समस्या प्रकरण

समस्या वर्णन

एका उत्पादनाच्या डीआयपीच्या वेव्ह क्रेस्ट वेल्डिंगनंतर, असे आढळून आले की नेटवर्क सॉकेटच्या फिक्स्ड फूटच्या सोल्डर प्लेटवर टिनची गंभीर कमतरता होती, जी एअर वेल्डिंगशी संबंधित होती.

समस्येचा परिणाम

परिणामी, नेटवर्क सॉकेट आणि पीसीबी बोर्डची स्थिरता खराब होते आणि उत्पादनाच्या वापरादरम्यान सिग्नल पिन फूटचा बल वापरला जाईल, ज्यामुळे शेवटी सिग्नल पिन फूटचे कनेक्शन होईल, ज्यामुळे उत्पादनाच्या कामगिरीवर परिणाम होईल आणि वापरकर्त्यांच्या वापरात बिघाड होण्याचा धोका निर्माण होईल.

समस्या विस्तार

नेटवर्क सॉकेटची स्थिरता खराब आहे, सिग्नल पिनची कनेक्शन कार्यक्षमता खराब आहे, गुणवत्तेच्या समस्या आहेत, त्यामुळे वापरकर्त्याला सुरक्षा धोके येऊ शकतात, अंतिम नुकसान अकल्पनीय आहे.

डीआयपी डिव्हाइस असेंब्ली विश्लेषण तपासणी

डीआयपी डिव्हाइस पिनशी संबंधित अनेक समस्या आहेत आणि अनेक महत्त्वाचे मुद्दे दुर्लक्षित करणे सोपे आहे, ज्यामुळे अंतिम स्क्रॅप बोर्ड तयार होतो. तर अशा समस्या एकदा आणि कायमच्या लवकर आणि पूर्णपणे कशा सोडवायच्या?

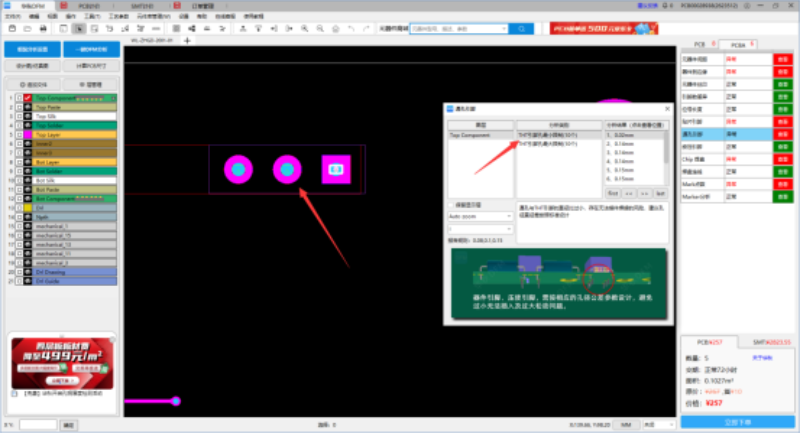

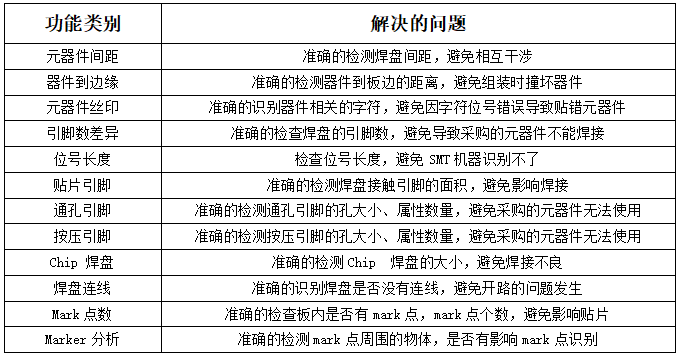

येथे, आमच्या CHIPSTOCK.TOP सॉफ्टवेअरचे असेंब्ली आणि विश्लेषण कार्य DIP उपकरणांच्या पिनवर विशेष तपासणी करण्यासाठी वापरले जाऊ शकते. तपासणी आयटममध्ये छिद्रांमधून पिनची संख्या, THT पिनची मोठी मर्यादा, THT पिनची लहान मर्यादा आणि THT पिनचे गुणधर्म समाविष्ट आहेत. पिनचे तपासणी आयटम मुळात DIP उपकरणांच्या डिझाइनमधील संभाव्य समस्यांना कव्हर करतात.

पीसीबी डिझाइन पूर्ण झाल्यानंतर, पीसीबीए असेंब्ली विश्लेषण फंक्शनचा वापर डिझाइनमधील दोष आगाऊ शोधण्यासाठी, उत्पादनापूर्वी डिझाइनमधील विसंगती सोडवण्यासाठी आणि असेंब्ली प्रक्रियेतील डिझाइन समस्या टाळण्यासाठी, उत्पादन वेळेत विलंब करण्यासाठी आणि संशोधन आणि विकास खर्च वाया घालवण्यासाठी केला जाऊ शकतो.

त्याच्या असेंब्ली विश्लेषण कार्यात १० प्रमुख आयटम आणि २३४ बारीक आयटम तपासणी नियम आहेत, जे डिव्हाइस विश्लेषण, पिन विश्लेषण, पॅड विश्लेषण इत्यादी सर्व संभाव्य असेंब्ली समस्यांचा समावेश करतात, जे अभियंते आगाऊ अंदाज लावू शकत नाहीत अशा विविध उत्पादन परिस्थिती सोडवू शकतात.

पोस्ट वेळ: जुलै-०५-२०२३