डीआयपी उपकरणांबद्दल, पीसीबी लोक काही जलद खड्डा थुंकत नाहीत!

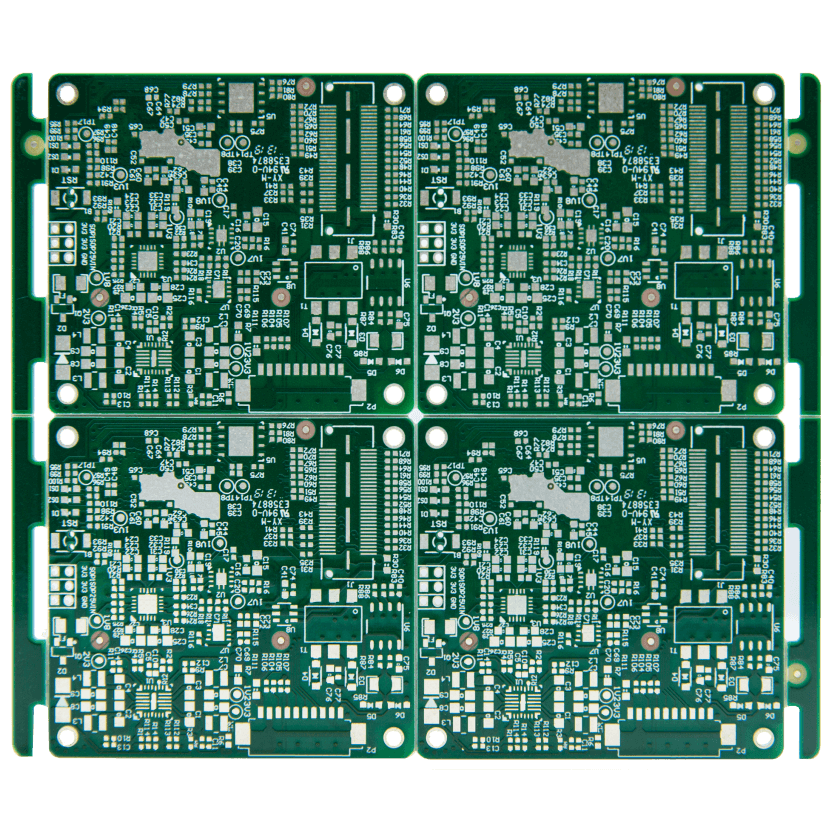

डीआयपी एक प्लग-इन आहे.अशा प्रकारे पॅकेज केलेल्या चिप्समध्ये पिनच्या दोन पंक्ती असतात, ज्याला डीआयपी स्ट्रक्चरसह चिप सॉकेटमध्ये थेट वेल्डेड केले जाऊ शकते किंवा समान संख्येच्या छिद्रांसह वेल्डिंग स्थितीत वेल्ड केले जाऊ शकते.पीसीबी बोर्ड छिद्र वेल्डिंग लक्षात घेणे खूप सोयीचे आहे, आणि मदरबोर्डशी चांगली सुसंगतता आहे, परंतु त्याचे पॅकेजिंग क्षेत्र आणि जाडी तुलनेने मोठी आहे, आणि पिन घालणे आणि काढण्याच्या प्रक्रियेत खराब होणे सोपे आहे, खराब विश्वासार्हता आहे.

डीआयपी हे सर्वात लोकप्रिय प्लग-इन पॅकेज आहे, अॅप्लिकेशन श्रेणीमध्ये मानक लॉजिक आयसी, मेमरी एलएसआय, मायक्रो कॉम्प्युटर सर्किट्स इ. स्मॉल प्रोफाइल पॅकेज (एसओपी), एसओजे (जे-टाइप पिन स्मॉल प्रोफाइल पॅकेज), टीएसओपी (पातळ लहान प्रोफाइल पॅकेज), व्हीएसओपी (खूप लहान प्रोफाइल पॅकेज), एसएसओपी (कमी केलेले एसओपी), टीएसएसओपी (पातळ कमी केलेले एसओपी) आणि एसओटी (स्मॉल प्रोफाइल ट्रान्झिस्टर), एसओआयसी (स्मॉल प्रोफाइल इंटिग्रेटेड सर्किट), इ.

- पीसीबी पॅकेज होल डिव्हाइसपेक्षा मोठे आहे

पीसीबी प्लग-इन होल आणि पॅकेज पिन होल वैशिष्ट्यांनुसार काढले जातात.प्लेट बनवताना छिद्रांमध्ये कॉपर प्लेटिंगची आवश्यकता असल्यामुळे, सामान्य सहनशीलता अधिक किंवा उणे 0.075 मिमी असते.PCB पॅकेजिंग होल भौतिक उपकरणाच्या पिनपेक्षा खूप मोठे असल्यास, यामुळे उपकरण सैल होणे, अपुरा टिन, एअर वेल्डिंग आणि इतर गुणवत्तेच्या समस्या उद्भवतील.

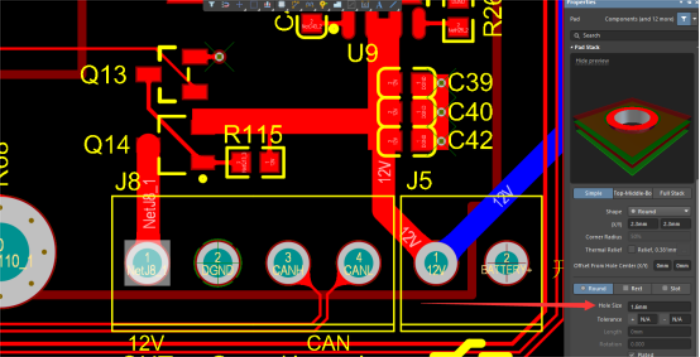

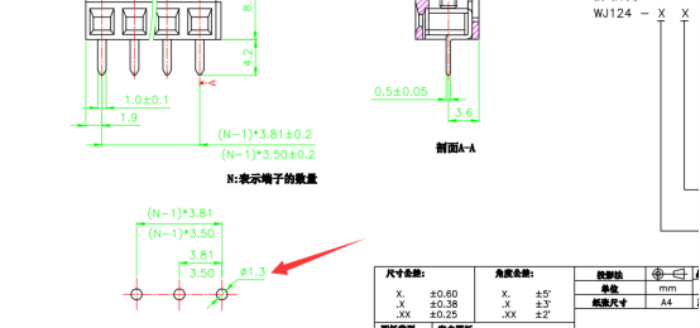

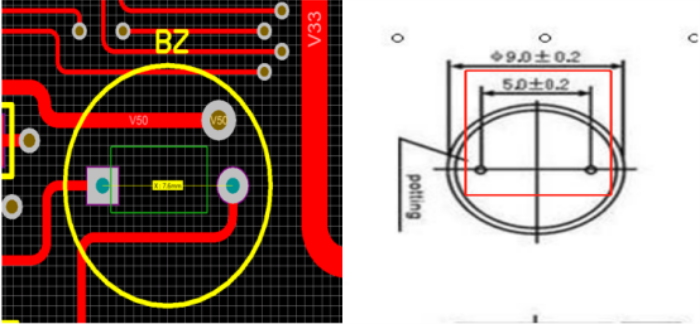

खालील आकृती पहा, WJ124-3.81-4P_WJ124-3.81-4P (KANGNEX) डिव्हाइस पिन वापरून 1.3mm आहे, PCB पॅकेजिंग होल 1.6mm आहे, ओव्हर वेव्ह वेल्डिंग स्पेस टाइम वेल्डिंगसाठी छिद्र खूप मोठे आहे.

आकृतीशी संलग्न, डिझाइन आवश्यकतांनुसार WJ124-3.81-4P_WJ124-3.81-4P (KANGNEX) घटक खरेदी करा, पिन 1.3mm योग्य आहे.

- पीसीबी पॅकेज होल डिव्हाइसपेक्षा लहान आहे

प्लग-इन, परंतु विल होल नो कॉपर, जर ते सिंगल असेल आणि दुहेरी पॅनेल ही पद्धत वापरू शकतात, सिंगल आणि डबल पॅनेल्स बाह्य विद्युत वहन आहेत, सोल्डर प्रवाहकीय असू शकतात;मल्टीलेयर बोर्डचे प्लग-इन होल लहान आहे आणि PCB बोर्ड फक्त तेव्हाच रिमेक केले जाऊ शकते जेव्हा आतील लेयरमध्ये इलेक्ट्रिकल कंडक्शन असेल, कारण आतील लेयर कंडक्शन रीमिंग करून सुधारता येत नाही.

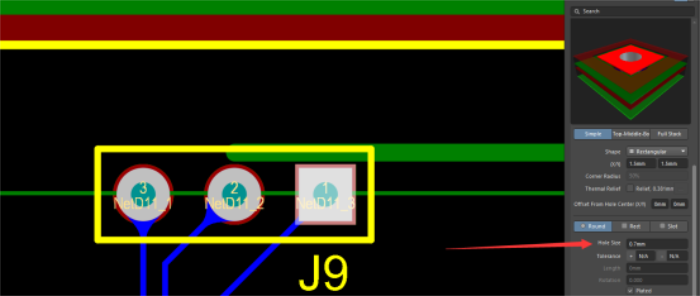

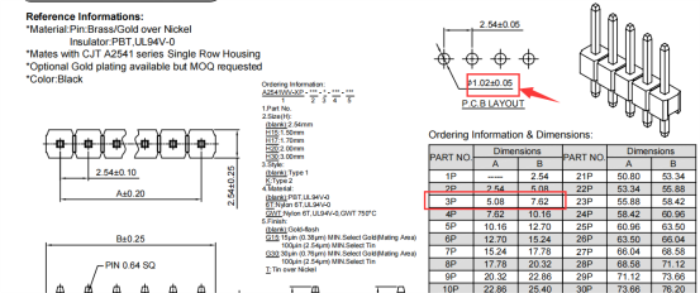

खालील आकृतीमध्ये दाखवल्याप्रमाणे, A2541Hwv-3P_A2541HWV-3P (CJT) चे घटक डिझाइनच्या गरजेनुसार खरेदी केले जातात.पिन 1.0mm आहे, आणि PCB सीलिंग पॅड होल 0.7mm आहे, परिणामी घालण्यात अयशस्वी होते.

A2541Hwv-3P_A2541HWV-3P (CJT) चे घटक डिझाइन आवश्यकतांनुसार खरेदी केले जातात.पिन 1.0mm योग्य आहे.

- पॅकेज पिन अंतर डिव्हाइस अंतरापेक्षा वेगळे आहे

डीआयपी उपकरणाच्या पीसीबी सीलिंग पॅडमध्ये फक्त पिनसारखेच छिद्र नसून पिनच्या छिद्रांमधील अंतर देखील आवश्यक आहे.पिन होल आणि डिव्हाइसमधील अंतर विसंगत असल्यास, समायोज्य फूट अंतर असलेल्या भागांशिवाय, डिव्हाइस घातले जाऊ शकत नाही.

खालील आकृतीत दाखवल्याप्रमाणे, PCB पॅकेजिंगचे पिन होल अंतर 7.6mm आहे, आणि खरेदी केलेल्या घटकांचे पिन होल अंतर 5.0mm आहे.2.6mm च्या फरकामुळे डिव्हाइस निरुपयोगी आहे.

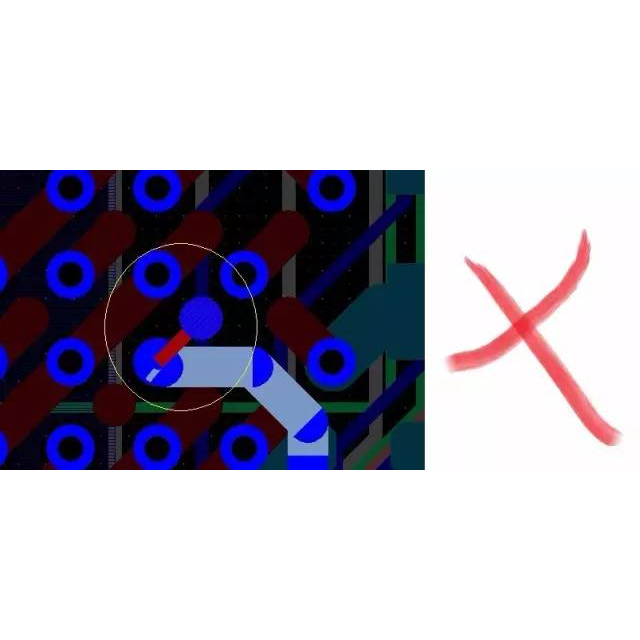

- पीसीबी पॅकेजिंग होल खूप जवळ आहेत

पीसीबी डिझाइन, रेखांकन आणि पॅकेजिंगमध्ये, पिन होलमधील अंतरावर लक्ष देणे आवश्यक आहे.जरी बेअर प्लेट तयार केली जाऊ शकते, पिनच्या छिद्रांमधील अंतर कमी आहे, तरंग सोल्डरिंगद्वारे असेंब्ली दरम्यान टिन शॉर्ट सर्किट करणे सोपे आहे.

खालील चित्रात दाखवल्याप्रमाणे, लहान पिन अंतरामुळे शॉर्ट सर्किट होऊ शकते.सोल्डरिंग टिनमध्ये शॉर्ट सर्किट होण्याची अनेक कारणे आहेत.डिझाईनच्या शेवटी एकत्र येण्याला आगाऊ प्रतिबंधित केले असल्यास, समस्यांचे प्रमाण कमी केले जाऊ शकते.

- समस्येचे वर्णन

डीआयपी उत्पादनाच्या वेव्ह क्रेस्ट वेल्डिंगनंतर, असे आढळून आले की नेटवर्क सॉकेटच्या स्थिर पायाच्या सोल्डर प्लेटवर टिनची गंभीर कमतरता आहे, जी एअर वेल्डिंगशी संबंधित आहे.

- समस्या प्रभाव

परिणामी, नेटवर्क सॉकेट आणि पीसीबी बोर्डची स्थिरता बिघडते आणि उत्पादनाच्या वापरादरम्यान सिग्नल पिन फूटची शक्ती वापरली जाईल, ज्यामुळे शेवटी सिग्नल पिन फूटचे कनेक्शन होईल आणि उत्पादनावर परिणाम होईल. कार्यप्रदर्शन आणि वापरकर्त्यांच्या वापरामध्ये अपयशाचा धोका निर्माण करणे.

- समस्या विस्तार

नेटवर्क सॉकेटची स्थिरता खराब आहे, सिग्नल पिनची कनेक्शन कामगिरी खराब आहे, गुणवत्ता समस्या आहेत, त्यामुळे वापरकर्त्यासाठी सुरक्षितता धोके येऊ शकतात, अंतिम नुकसान अकल्पनीय आहे.

- डीआयपी उपकरण पिनशी संबंधित अनेक समस्या आहेत आणि अनेक मुख्य मुद्दे दुर्लक्षित करणे सोपे आहे, परिणामी अंतिम स्क्रॅप बोर्ड आहे.तर अशा समस्या एकदा आणि सर्वांसाठी त्वरीत आणि पूर्णपणे कसे सोडवायचे?

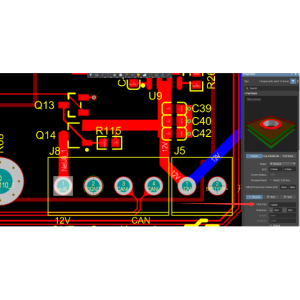

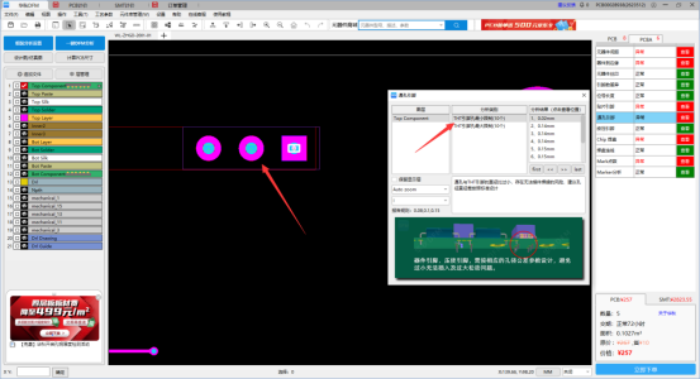

- येथे, आमच्या CHIPSTOCK.TOP सॉफ्टवेअरचे असेंब्ली आणि विश्लेषण कार्य DIP उपकरणांच्या पिनवर विशेष तपासणी करण्यासाठी वापरले जाऊ शकते.तपासणी आयटममध्ये छिद्रांद्वारे पिनची संख्या, THT पिनची मोठी मर्यादा, THT पिनची लहान मर्यादा आणि THT पिनची वैशिष्ट्ये समाविष्ट आहेत.पिनच्या तपासणी आयटममध्ये मुळात डीआयपी उपकरणांच्या डिझाइनमधील संभाव्य समस्यांचा समावेश होतो.

- PCB डिझाइन पूर्ण झाल्यानंतर, PCBA असेंब्ली अॅनालिसिस फंक्शनचा वापर डिझाईनमधील दोष अगोदर शोधण्यासाठी, उत्पादनापूर्वी डिझाइनमधील विसंगती सोडवण्यासाठी आणि असेंबली प्रक्रियेतील डिझाइन समस्या टाळण्यासाठी, उत्पादनाचा वेळ विलंब आणि संशोधन आणि विकास खर्च वाया घालवण्यासाठी वापरला जाऊ शकतो.

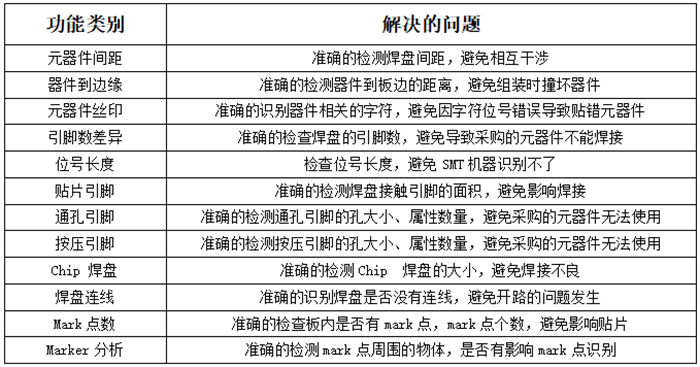

- त्याच्या असेंबली विश्लेषण फंक्शनमध्ये 10 प्रमुख वस्तू आणि 234 बारीकसारीक वस्तूंचे निरीक्षण नियम आहेत, ज्यामध्ये सर्व संभाव्य असेंबली समस्या समाविष्ट आहेत, जसे की डिव्हाइस विश्लेषण, पिन विश्लेषण, पॅड विश्लेषण, इ, जे विविध प्रकारच्या उत्पादन परिस्थितींचे निराकरण करू शकतात ज्याची अभियंता आगाऊ अपेक्षा करू शकत नाहीत.